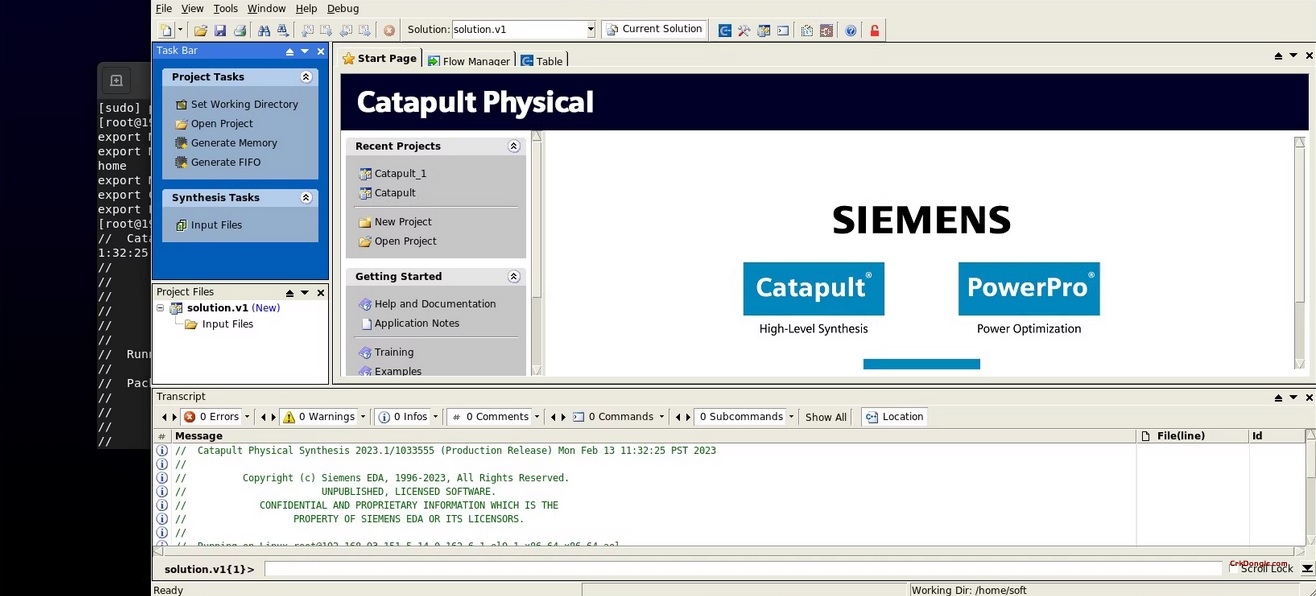

Siemens Catapult HLS 2025 for Linux | High-Level Synthesis (HLS) & Algorithm-to-RTL Platform

Siemens Catapult HLS 2025 for Linux is a leading-edge, Linux-native High-Level Synthesis platform that transforms algorithm specifications written in C++, SystemC, or MATLAB directly into optimized, production-quality RTL (VHDL/Verilog). It dramatically accelerates the design of complex ASICs and FPGAs by raising the abstraction level.

Core Functionality Overview:

-

Algorithmic C/C++ to RTL Synthesis: Synthesizes untimed C++, SystemC, and ANSI C++ models into area, performance, and power-optimized RTL, enabling hardware architects to explore micro-architectures at a high level.

-

Advanced Micro-Architecture Exploration & Verification: Provides interactive analysis and optimization tools for exploring different implementations (pipelining, loop unrolling, memory architectures) and includes formal equivalence checking to ensure the generated RTL matches the source algorithm.

-

Integrated Design Flow & IP Generation: Features seamless integration with Siemens RTL simulation and verification tools, and automatically generates synthesizable IP blocks with associated verification testbenches and documentation.