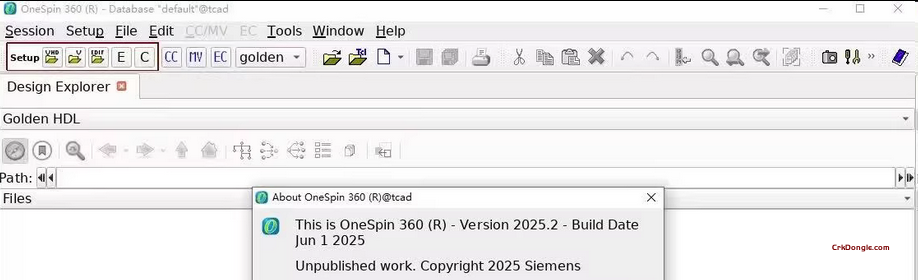

Questa OneSpin Static Formal 2025: The Exhaustive Verification Platform for Zero-Defect Designs

Questa OneSpin Static Formal 2025 represents the industry’s most advanced static formal verification platform, designed for engineers who require mathematical certainty in their ASIC, FPGA, and IP designs. Unlike traditional simulation, which tests only a subset of possible scenarios, static formal verification uses rigorous mathematical proof techniques to exhaustively analyze a design against its specifications. This makes it an indispensable tool for verifying safety-critical hardware in automotive (ISO 26262), aerospace, and medical applications where a single undetected bug can have catastrophic consequences.

Core Technology & Key Capabilities:

1. Formal Property Verification (FPV)

This is the flagship application, enabling engineers to prove that a design’s behavior matches its intended specification under all possible inputs and states.

-

Assertion-Based Verification: Users write formal properties (assertions) in SystemVerilog Assertions (SVA) or PSL to define correct behavior. The tool then mathematically proves these properties are always true or finds a concrete counterexample trace showing a bug.

-

Automatic Proof Engines: Incorporates multiple, high-capacity formal engines (like IC3/PDR, interpolation, and BDD-based) to automatically tackle complex proofs without manual guidance.

-

Coverage Closure: Provides 100% functional coverage for verified properties, eliminating the coverage uncertainty inherent in simulation-based verification.

2. Equivalence Checking (EC)

A critical step in any design flow to ensure functional consistency between different design representations.

-

RTL-to-Gate Level: Exhaustively proves that a synthesized netlist is functionally identical to its original RTL source, catching synthesis or constraint errors.

-

Gate-to-Gate Level: Verifies that a physically optimized netlist (after clock tree synthesis, scan insertion) remains equivalent to its pre-optimized version.

-

Sequential & Combinational: Handles both combinational logic and complex sequential logic with internal state registers.

3. Advanced RTL Analysis & Automated Apps

OneSpin goes beyond basic formal engines with intelligent applications that find bugs without requiring users to write complex properties.

-

Automatic Bug Hunting: Apps like Verix™ automatically check for common designer errors (dead code, unreachable states, bus conflicts, FSM deadlocks) directly on RTL, finding bugs early in the design cycle.

-

Safety & Security Verification: Dedicated apps can formally verify that safety mechanisms (like lockstep cores, ECC) work as specified and that security-critical assets cannot be accessed through unauthorized paths.

4. Seamless Integration & Debug Environment

-

Industry-Standard Interfaces: Integrates with Siemens EDA’s Questa™ simulation suite and other leading design environments, supporting common design and verification languages (SystemVerilog, VHDL, UPF).

-

Visual Debugger: When a property fails, it provides a full, waveform-like counterexample trace that visually steps through the exact scenario leading to the bug, drastically reducing debug time.