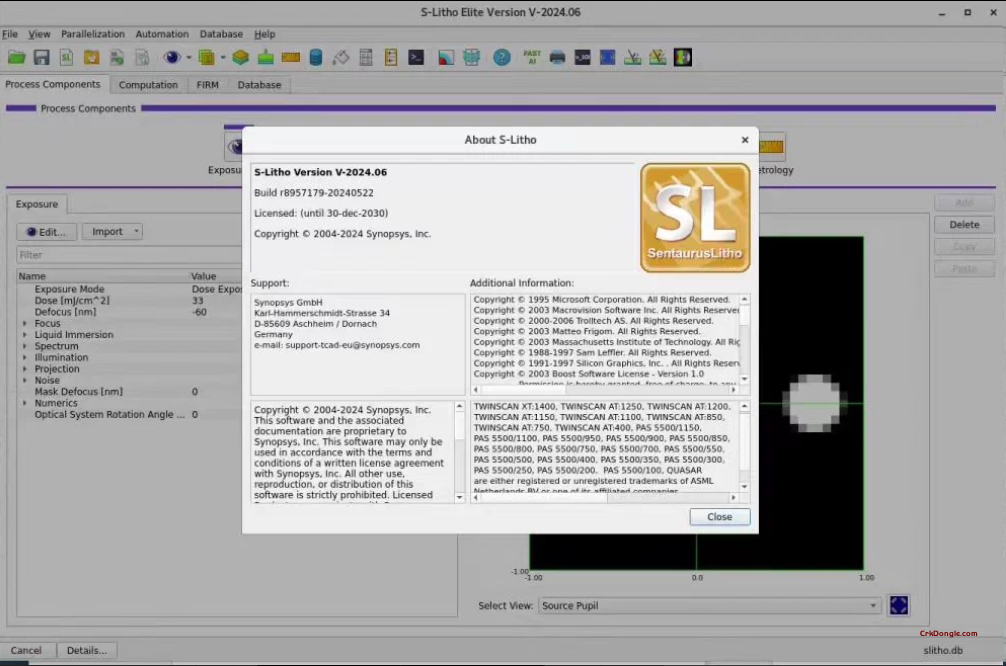

Synopsys S-Litho 2025: The Lithography Simulation Workbench for Advanced Nodes

Synopsys S-Litho 2025 is a high-performance lithography simulation and analysis tool within the Synopsys EDA ecosystem, critical for ensuring the manufacturability of integrated circuits at sub-wavelength process nodes. It enables chip designers and process engineers to predict and correct distortions that occur when nanometer-scale circuit patterns are transferred onto silicon wafers using optical lithography.

Core Function: Predicting and Correcting Pattern Distortions

Its primary function is to simulate the complex physics of light diffraction and resist chemistry to model the final printed pattern on a wafer. This predictive capability is the foundation for applying essential Resolution Enhancement Techniques (RET) that make leading-edge chip manufacturing possible.

Key Functions:

-

Full-Chip Lithography Simulation: Rapidly simulates the aerial image and resist patterning process across an entire chip layout to identify printing hotspots and critical areas.

-

Optical Proximity Correction (OPC): Provides a core environment for developing and verifying OPC recipes, which pre-distort the design mask to compensate for optical effects, ensuring the printed wafer pattern matches the intended design.

-

Resolution Enhancement Technique (RET) Analysis: Supports the analysis and implementation of advanced RETs such as Sub-Resolution Assist Features (SRAFs), Phase-Shift Masks (PSM), and Source-Mask Optimization (SMO).

-

Hotspot Detection & Process Window Analysis: Identifies layout patterns prone to failure and analyzes the robustness of the design across variations in focus and exposure dose.