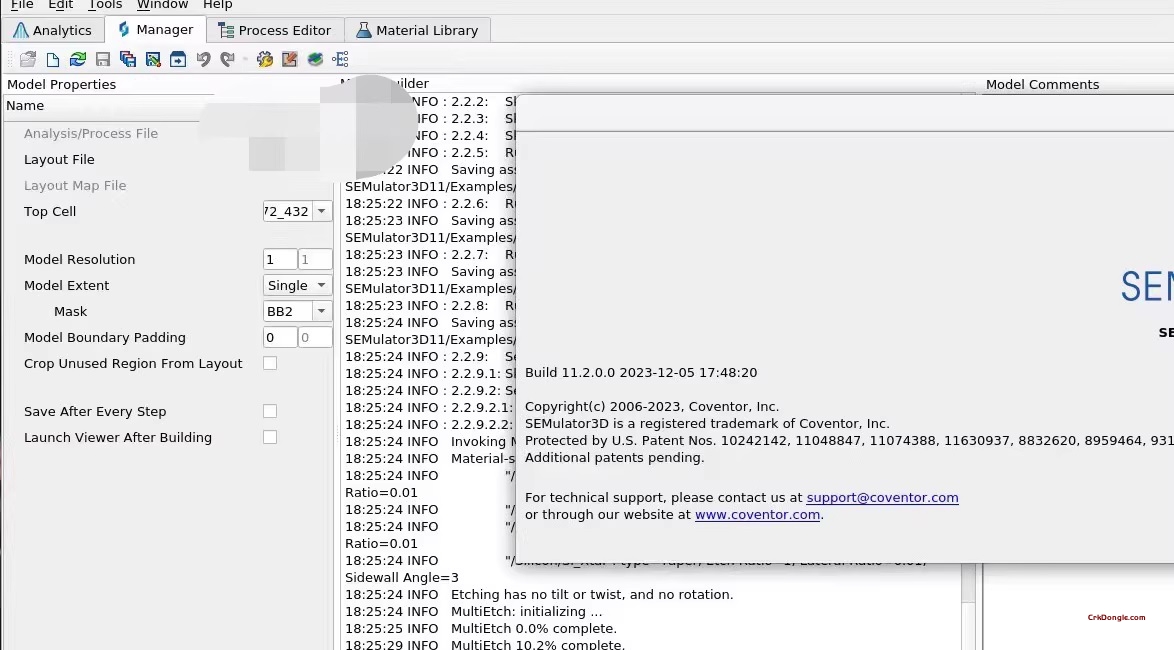

Coventor SEMulator3D 11.2: The Definitive Platform for 3D Semiconductor Virtual Fabrication

Coventor SEMulator3D 11.2 is the industry-leading software solution for virtual fabrication and predictive process modeling of the world’s most advanced 3D semiconductor devices and advanced packaging architectures. As part of the Ansys portfolio, it enables process engineers, integration engineers, and device designers to build and analyze a complete digital twin of the complex 3D manufacturing process flow. By emulating hundreds of sequential process steps (deposition, etch, CMP, lithography), SEMulator3D predicts the exact 3D geometry, electrical parasitics, and structural variations that will result on the silicon wafer, long before committing to costly and time-consuming fab experiments.

Core Philosophy: “Fab-in-a-Box” for Predictive Process Development

SEMulator3D’s power lies in its rule-based, voxel (3D pixel) modeling approach. Instead of simulating fundamental physics at the atomic level, it applies calibrated, empirical process models that emulate the outcome of each fab step with high accuracy and incredible speed. This allows users to run full “virtual DOEs” (Design of Experiments), exploring thousands of process variations and design-technology co-optimization (DTCO) scenarios to identify the optimal integration scheme for yield, performance, and reliability.

Key Application Areas & Analysis Modules:

1. 3D Memory & Logic Process Emulation

-

3D NAND & DRAM Development: The essential tool for designing and optimizing vertical memory stacks, including staircase formation, channel hole etch, and word line plug. It predicts critical metrology like CD (critical dimension), sidewall angle, and overlay errors.

-

FinFET & Gate-All-Around (GAA) Nanosheet Modeling: Models the complete 3D formation of advanced logic transistors, from fin patterning and dummy gate removal to spacer formation and metal gate fill, predicting shape-dependent electrical effects.

2. Advanced Packaging & Heterogeneous Integration

-

2.5D/3D Integration: Models through-silicon vias (TSVs), micro-bumps, redistribution layers (RDL), and silicon interposers for 3D ICs and chiplets.

-

Fan-Out Wafer-Level Packaging (FOWLP): Simulates the complex molding, warpage, and RDL formation processes in advanced packaging.

3. Predictive Metrology & Defect Analysis

-

Virtual Metrology: Generates synthetic SEM (Scanning Electron Microscope) and TEM (Transmission Electron Microscope) cross-section images from the 3D model, matching what would be measured in the fab.

-

Defect and Yield Prediction: Identifies potential failure points, such as pinch-offs during deposition, voids during fill, or bridging due to misalignment, enabling proactive process correction.

4. Parasitic Extraction & Electrical Analysis

-

Automated RC Extraction: Directly from the generated 3D structure, it extracts accurate resistance and capacitance parasitics, which are critical for predicting circuit performance (speed, power) and signal integrity in dense 3D layouts.

-

Stress & Mechanical Analysis: Can interface with other Ansys solvers to analyze stress-induced mobility effects and mechanical reliability.