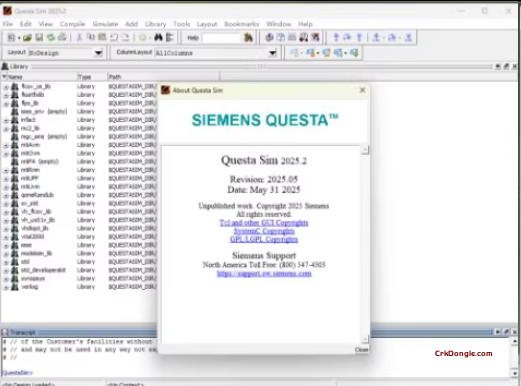

Siemens Questa Sim 2025.2: The Core Engine for Next-Generation Verification

Siemens Questa Sim 2025.2 stands as the high-performance, mixed-language verification engine at the heart of the Siemens EDA verification suite. Engineered for the immense complexity of modern System-on-Chip (SoC) and FPGA designs, it provides a robust and scalable environment for simulation, debug, and coverage closure. This release focuses on enhanced performance, deeper debug capabilities, and expanded support for the latest verification methodologies, making it an indispensable tool for verification engineers tasked with ensuring first-pass silicon success in cutting-edge applications like AI accelerators, automotive SoCs, and high-performance computing.

Core Technology & Key Capabilities:

1. High-Performance, Mixed-Language Simulation

-

Native Multi-Language Support: Delivers seamless, high-performance simulation of designs and testbenches written in SystemVerilog, VHDL, Verilog, and e language, all within a single, unified kernel.

-

Advanced Compilation & Runtime Optimizations: Incorporates intelligent compilation technologies and runtime algorithms to handle billion-gate designs efficiently, reducing simulation turnaround time.

-

Transaction-Level Modeling (TLM) 2.0: Provides built-in support for SystemC TLM-2.0, enabling fast architectural modeling and virtual platform integration for early software development.

2. Universal Verification Methodology (UVM) Acceleration

-

Native UVM Support: Offers optimized, native support for the UVM 1.2 and IEEE 1800.2 standards, providing the highest performance for constrained-random, reusable testbench execution.

-

UVM Debug & Analysis: Includes specialized debug views and analysis tools for UVM constructs (sequences, components, configuration, phase scheduling) to quickly pinpoint issues in complex testbench environments.

3. Advanced Debugging & Analysis Environment (Questa SIM Debug)

-

Intuitive Multi-Window Debugger: Features a powerful graphical debugger with synchronized source code, waveform, schematic, and listing views for rapid root-cause analysis.

-

Dynamic Debug & Probing: Allows engineers to interactively query signal values, set new breakpoints, and force signals during simulation runtime without recompilation.

-

Automated Debug Assistants: Includes intelligent assistants that can automatically trace the root cause of common problems like X-propagation, deadlock, and memory access violations.

4. Comprehensive Functional Coverage Closure

-

Unified Coverage Database: Integrates code coverage, functional coverage (from SystemVerilog covergroups), and user-defined metrics into a single database, providing a clear view of overall verification progress.

-

Coverage Analysis & Visualization: Advanced tools for analyzing coverage holes, identifying exclusions, and generating actionable reports to drive the verification plan to completion.

5. Verification IP (VIP) & Ecosystem Integration

-

Broad VIP Catalog: Works seamlessly with the extensive Siemens Questa Verification IP library for standard interfaces (PCIe, USB, DDR, Ethernet, AMBA), accelerating testbench creation.

-

Seamless Tool Flow: Integrates directly with other Siemens EDA solutions, including Questa Formal (for property checking) and Veloce® hardware emulation platforms, enabling a smooth shift-left verification flow.