Cadence Virtuoso IC251: The Definitive Platform for Precision Custom IC Design

Cadence Virtuoso IC251 represents the cornerstone of the modern analog, mixed-signal, RF, and custom digital integrated circuit (IC) design flow. As the industry’s most trusted and comprehensive custom design platform, it provides an integrated, end-to-end environment where design architects and layout engineers can conceive, simulate, implement, and validate the most intricate and performance-sensitive circuits. From high-speed SerDes PHYs and RF transceivers to precision data converters and sensitive analog front-ends, Virtuoso IC251 offers the depth of control, accuracy, and tool integration required to push the boundaries of silicon performance.

Core Workflow & Key Modules:

1. Design Entry & Capture

-

Schematic Editor: An intuitive and powerful environment for capturing complex hierarchical circuits, from top-level blocks down to individual transistors. Supports advanced connectivity and design management.

-

Analog Design Environment (ADE): The central cockpit for simulation setup and analysis. It provides a streamlined interface to configure tests, manage process corners, and visualize results from the industry-leading Spectre® simulation engine.

2. High-Precision Circuit Simulation & Analysis

-

Spectre Simulation Suite: Integrated directly within Virtuoso, this engine delivers gold-standard SPICE-level accuracy for analog and RF circuits. It includes fast SPICE options for large blocks and specialized solvers for RF and noise analysis.

-

Multi-Mode Simulation: Supports everything from basic DC operating point and transient analysis to advanced parametric sweeps, noise, stability (pz), and harmonic balance (for RF).

-

Interactive Debug & Visualization: Live probes and advanced plotting within ADE allow engineers to instantly analyze waveforms, calculate derivatives (gm, gain), and debug circuit behavior in real-time.

3. Physical Layout Implementation

-

Virtuoso Layout Suite: The industry-standard editor for creating full-custom, high-density IC layouts. It offers pixel-precise control over every polygon, essential for matching and optimizing analog performance.

-

Parameterized Cells (PCells): Smart, programmable layout cells that automatically generate correct geometry based on parameters (like transistor width/length), ensuring design rule correctness and dramatically speeding up layout creation.

-

Advanced Routing & Editing: Features shape-based editing, constraint-driven routing for matched groups, and in-design design rule checking (DRC) to catch errors during creation.

4. Verification & Signoff

-

Real-Time DRC/LVS: Deep integration with the Cadence Pegasus™ and Quantus™ platforms enables real-time physical and electrical verification. Engineers can run incremental DRC and layout-versus-schematic (LVS) checks without leaving the layout environment.

-

Electromagnetic (EM) Analysis: For critical RF components like inductors and transmission lines, Virtuoso links to EM solvers (like Clarity™) to accurately model parasitic effects and ensure first-pass silicon success.

5. Extended Capabilities for Modern Design

-

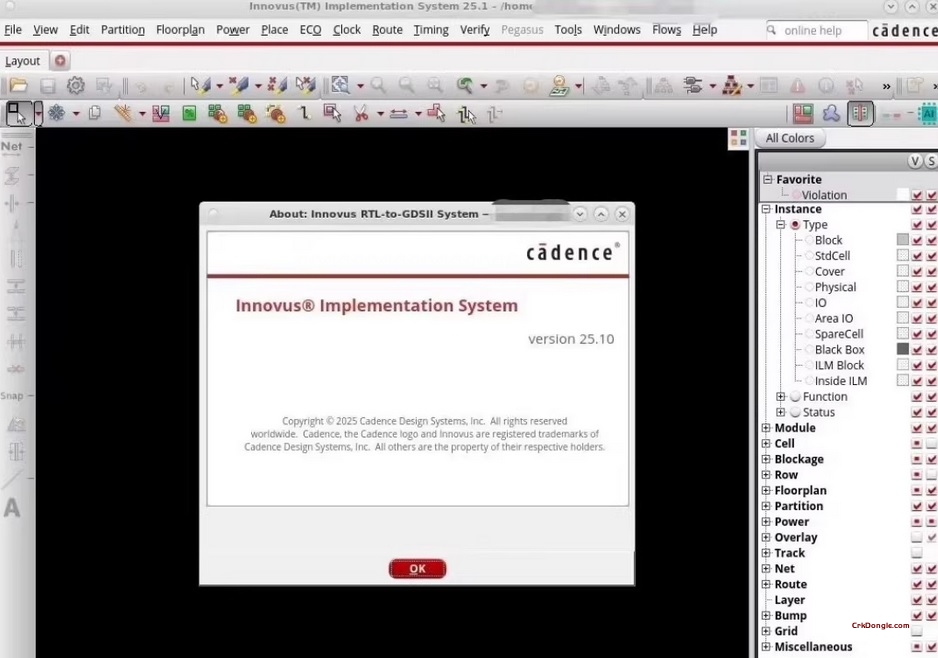

Mixed-Signal Implementation: Provides methodologies and interfaces for integrating custom analog blocks with digital logic from other Cadence implementation platforms (like Innovus™).

-

Design for Manufacturing (DFM): Incorporates yield and reliability analysis tools to check for lithography hotspots and improve manufacturability.