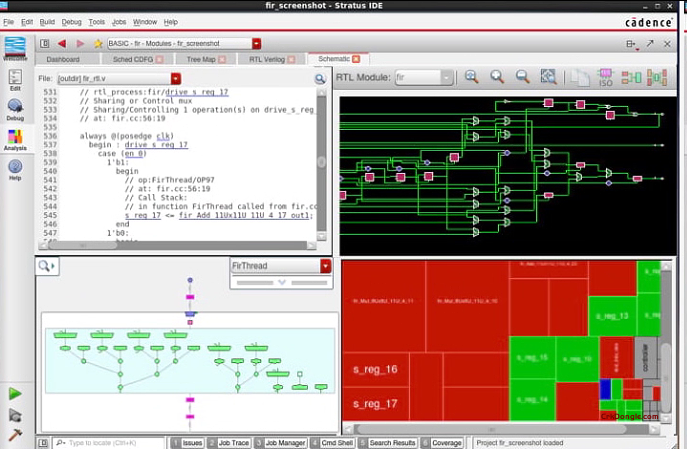

Cadence Stratus 2025: The High-Level Synthesis Powerhouse for RTL Generation

Cadence Stratus 2025 is a premier high-level synthesis (HLS) platform that fundamentally transforms the digital design workflow. It empowers hardware architects and design engineers to describe complex functionality and algorithms at a high abstraction level—using C++, SystemC, or MATLAB—and then automatically synthesize this behavioral description into optimized, high-quality, and cycle-accurate RTL (Verilog/VHDL). By elevating the starting point of design, Stratus dramatically increases productivity, enables architectural exploration, and accelerates the development of sophisticated IP for applications in AI/ML acceleration, advanced DSP, image processing, and communication systems.

Core Technology & Key Capabilities:

1. High-Abstraction Design Entry & Synthesis

-

C++ & SystemC Synthesis: Accepts industry-standard ANSI C++ and SystemC as input, allowing algorithms developed by software engineers to be directly targeted for hardware implementation.

-

Behavioral- to RTL-Level Transformation: Automatically handles the complex mapping of loops, arrays, functions, and data types into finite state machines (FSMs), datapaths, and memory structures, generating synthesizable RTL code.

-

Algorithmic IP Creation: Enables the rapid creation of reusable, high-performance IP blocks directly from algorithmic models, bridging the gap between system architects and RTL designers.

2. Extensive Design Space Exploration & Optimization

This is where Stratus provides its most significant value, allowing designers to explore trade-offs without manual RTL rewrites.

-

Automatic & Guided Optimization: Users can apply different optimization directives (pipeline, unroll, merge, inline) to specific parts of the code and instantly see the impact on area, latency, and throughput in detailed QoR (Quality of Results) reports.

-

Multi-Scenario Analysis: Enables the creation and comparison of multiple micro-architecture implementations from a single source, facilitating the selection of the optimal design point for power, performance, and area (PPA) goals.

3. Verification & Validation Integrity

A key strength of Stratus is its integrated verification flow, which ensures the synthesized RTL matches the original high-level intent.

-

C-to-RTL Formal Equivalence Checking: Mathematically proves the functional equivalence between the input C++/SystemC model and the generated RTL, eliminating functional bugs introduced during synthesis.

-

Seamless Testbench Re-use: Automatically generates the infrastructure to reuse the original C++ testbench to verify the synthesized RTL in simulation, ensuring consistency and saving months of verification effort.

-

Integration with Industry Simulators: Works directly with leading simulation environments (like Xcelium™) for fast, co-simulated validation.

4. Quality of Results & Production-Ready RTL

-

High-Quality RTL Generation: Produces clean, readable, and efficient RTL code that integrates smoothly into downstream logic synthesis and place-and-route flows.

-

Constraint & Interface Synthesis: Automatically generates timing constraints and supports the creation of complex bus interfaces (like AMBA AXI4), ensuring the IP is ready for system-level integration.

Who Should Use This Platform?

-

Hardware Architects & Algorithm Developers designing complex data paths for AI inference, computer vision, wireless basebands, or video codecs.

-

Digital Design & RTL Engineers seeking to drastically improve productivity and explore optimal micro-architectures for performance-critical blocks.

-

FPGA Developers needing to rapidly prototype and implement high-performance algorithms on programmable logic.

-

System-on-Chip (SoC) Teams looking to accelerate IP creation and improve overall project schedules.