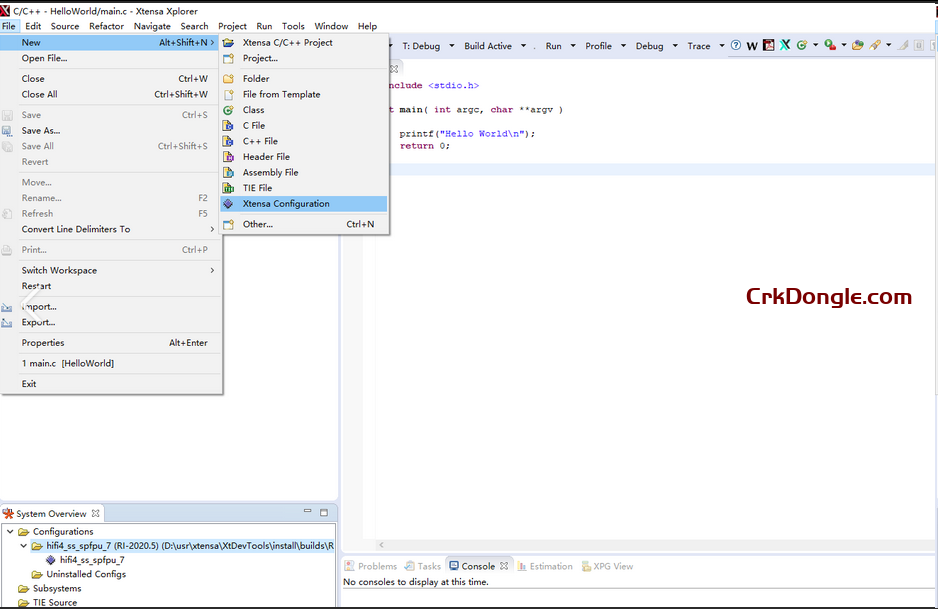

Cadence Xtensa Xplorer is a comprehensive integrated development environment (IDE) for the Tensilica Xtensa processor family, enabling designers to configure, customize, and optimize extensible 32-bit RISC processors and DSPs for energy-efficient SoCs in applications like AI/ML, automotive, IoT, and audio processing. Built on an Eclipse-based GUI, it provides a unified platform for hardware generation, software development, simulation, debugging, and profiling. Xplorer automates the creation of tailored processors using the Xtensa Processor Generator, integrating with EDA flows for RTL synthesis, verification, and integration. It supports multi-core systems, custom instructions via TIE (Tensilica Instruction Extension), and seamless transitions from ISS (Instruction Set Simulator) to RTL, FPGA, or silicon.

Version 11.1.5, released in mid-2025 as part of the ongoing Xtensa toolkit evolution, focuses on enhanced AI workload support, improved multi-processor coherence, and streamlined integration with Cadence’s broader EDA ecosystem (e.g., Genus synthesis and Innovus place-and-route). This patch release addresses bug fixes, performance tweaks for large-scale simulations, and expanded compatibility with Zephyr RTOS and NXP MCUs, building on the LX7/LX8 processor cores for generative AI and edge computing. As of October 13, 2025, it’s the latest stable version, available via Cadence’s Tensilica Tools portal for licensed users.

Key Features of Xtensa Xplorer 11.1.5

- Processor Configuration and Generation: Xtensa Processor Generator creates hardware designs with matching software tools, including compilers and ISS. Supports profiling, hot-spot analysis, and custom extensions without manual pipelining.

- Software Development Toolkit (SDK): High-performance C/C++ compiler (XCC) with SIMD/VLIW mapping, no assembly required. Includes DSP libraries, examples, and OS support (e.g., FreeRTOS, Zephyr).

- Simulation and Modeling: Cycle-accurate ISS, XTensa Modeling Protocol (XTMP) for multi-processor subsystems, and SystemC integration for early architecture exploration.

- Debug and Trace: xt-gdb for JTAG debugging, PC trace, code coverage, and multi-core support. Compatible with SEGGER J-Link probes and real-time trace tools.

- AI/ML Optimizations: Enhanced TIE for custom neural network instructions; wizards for ports/queues in DSP pipelines.

- Ecosystem Integration: Links with Cadence tools for functional safety (e.g., FlexLock, DCLS), windowed watchdog timers, and SoC verification.

What’s New in 11.1.5?

- Performance Enhancements: Up to 15% faster compilation for multi-core AI models; optimized threading for hybrid MPI in large simulations.

- RTOS and MCU Support: Improved add-ons for Zephyr Project and NXP i.MX RT series (e.g., EVK-MIMXRT685), including LSP (Linker Support Package) customization for memory mapping.

- AI and Safety Focus: New pre-built extensions for generative AI tasks; expanded fault injection for ISO 26262 compliance in automotive designs.

- Usability Updates: Refined NanoLab-like GUI for Linux/Windows; better GLX support for graphics; automated license key generation for SDK downloads.

- Training and Resources: Updated labs in the Xtensa LX Fundamentals course cover 11.1.5 features like installation, first programs, and optimization.