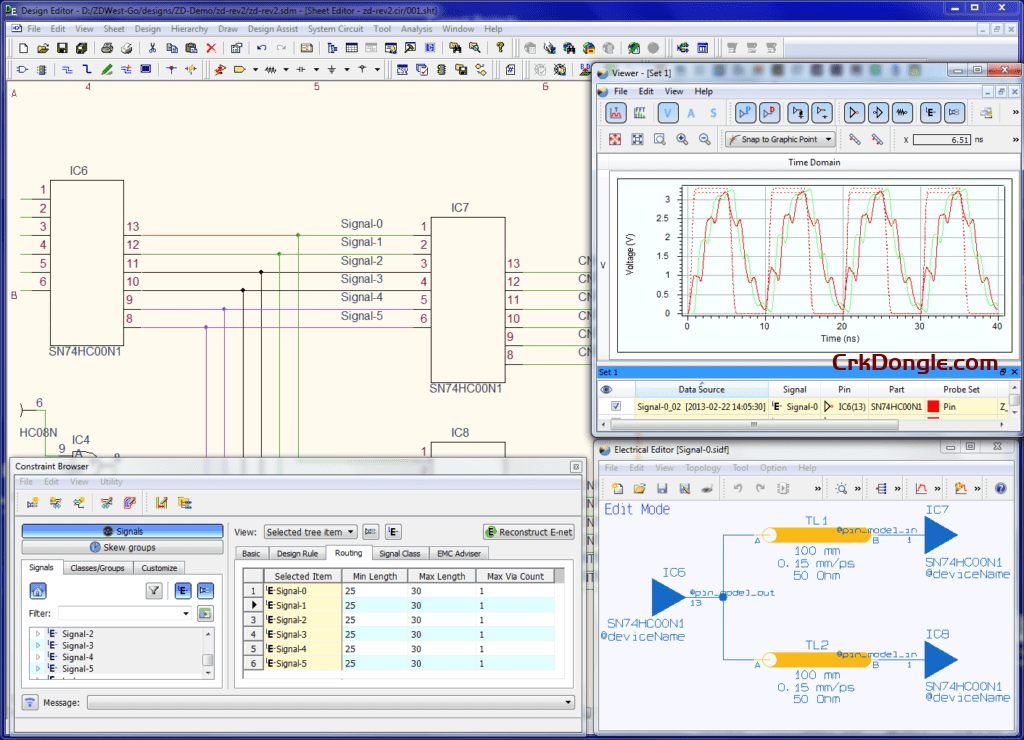

Design Gateway is a platform for logical electronic circuit design and verification of single and multi-board system-level designs. It supports a true system-level PCB design in which individual circuits can be represented and connected as blocks. The platform enables engineers to manage signal continuity (interconnects) at the system level rather than just at the design level, allowing for an evaluation of board-to-board signal continuity.

Zuken CR-8000 Release 2025 brings enhanced simulation workflows, strengthened multi-board 3D co-design, expanded AI-assisted routing, and tighter PLM synchronization for faster development cycles, greater design reliability, and a more connected enterprise design flow. Key areas of improvement include automation, to accelerate and standardize complex layout and verification tasks; embedded intelligence, enabling real-time decision-making during schematic capture, placement, routing, and simulation; and design convergence, integrating system planning, PCB layout, packaging, and mechanical constraints within a single collaborative environment.

Advanced Constraint Propagation

Release 2025 improves the transfer of timing, skew, and delay constraints between Design Gateway (schematics) and Design Force (physical layout), offering the following benefits:

- Seamless implementation of specifications from system planning to physical layout

- Consistent application of constraints for delays, skew, and topologies in high-speed interfaces (e.g., DDR, PCIe, SerDes)

- Reduced need for manual alignment, lowering the risk of inconsistent constraint definitions

Automated Placement of Decoupling Capacitors

A new feature in CR-8000 Design Force enables rule-based placement and routing of decoupling capacitors according to power integrity constraints—ensuring optimal proximity to power pins and minimal loop areas.

- Targeted noise suppression in critical power networks

- Optimized bypass structures through impedance and loop-area control

- Reliable timing in complex, high-density designs—without manual errors

Meshplane and Via Management

CR-8000 Design Force introduces several critical enhancements to meshplane and via handling, targeting both signal integrity and manufacturability in dense, multilayer designs:

- Meshplanes update automatically when routing on adjacent layers is modified, eliminating the need for manual regeneration and reducing post-layout cleanup.

- Reinforcing vias can be placed systematically on a design-defined grid, improving mechanical strength and EMI shielding, especially in large or flexible PCBs.

- Mesh cutout spacing is now editable through the Rule Editor, enabling finer control over edge clearance and adherence to fab-specific design rules.